1.概述

本文是用于记录vivado中DDS IP核输出任意频率,与任意相位的关键点,即频率控制字与相位控制字的设置。

2.参考文档《pg141-dds-compiler》

《基于FPGA的DDS任意波形发生器设计 - yfwblog - 博客园》

3.DDS原理根据傅立叶变换定理可知,任何周期信号都可以分解为一系列正弦或余弦信号之和,不失一般性,以正弦信号的产生为例详细说明直接数字频率合成技术的原理。比如一个频率为fc的正弦信号,其时域表

达式为:

其相位表达式为:

从两式可以看出,正弦信号是关于相位的一个周期函数,下图更加直观的描述相位与幅度的关系,16个相位与16个幅度值相对应,即每一个相位值对应一个幅度值,比如1100对应的相位为3π/2,对应的幅度值为-1.

相位和幅值的一一对应关系就好比存储器中地址和

存储内容的关系,如果把一个周期内每个相位对应的幅度值存入存储器当中,那么对于任意频率的正弦信号,在任意时刻,只要已知相位Φ(t),也就知道地址,就可通过查表得到s(t)。下图是DDS的基本结构框图:

相位累加器在每个时钟脉冲输入时,把频率控制字累加一次,相位累加器的输出数据就是信号的相位,用输出的数据作为波形存储器(ROM)的相位取样地址,这样就可以把存取在波形存储器内的波形抽样值经查找表查处,完成相位到幅值的转换。频率控制字相当于Φ(t)中的2πfc,相位控制字相当于Φ(t)中的θ0。

由于相位累加器字长的限制,相位累加器累加到一定值后,其输出将会溢出,这样波形存储器的地址就会循环一次,即意味着输出波形循环一周。故改变频率控制字即相位增量,就可以改变相位累加器的溢出时间,在时钟频率不变的条件下就可以改变输出频率。改变查表寻址的时钟频率,同样也可以改变输出波形的频率。

为了获得较高的频率分辨率,则只有增加相位累加器的字长N,故一般N都取值较大。但是受存储器容量的限制,存储器地址线的位数w不可能很大,一般都要小于N。这样存储器的地址线一般都只能接在相位累加器输出的高w位,而相位累加器输出余下的(N-W)个低位则只能被舍弃,这就是相位截断误差的来源。

DDS模块的输出频率fout是系统工作频率fc、相位累加器位数N及频率控制字K满足如下关系

频率分辨率,即频率的变化间隔

4.关键点

以下都是以一个IP核生成1路信号分析。

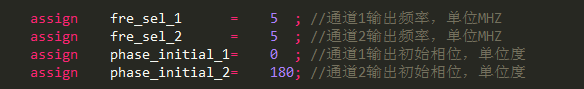

4.1 频率控制字分析频率控制字即相位增量,在datasheet中又叫PINC。其公式为:

Δθ:即相位增量,即频率控制字PINC;

Fout:即想要输出的频率;

Fclk:即输入IP的时钟,也是这个信号的采样时钟;

Bθ(n):为频率精度的位数,其计算公式如下,取位都为进位(以产生时钟为fclk=100MHZ,频率精度Δf为1HZ计算):

Δf:频率精度,即IP核设置钟的“Frequency Resolution”,在第5章会有标注。

4.2 相位控制字分析相位控制字即相位偏移量,在datasheet中又叫POFF。

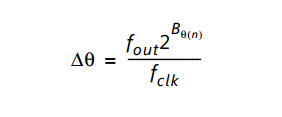

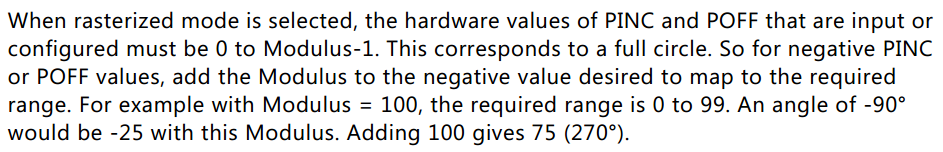

POFF在手册中没有给出一个公式,但给过一段话,如下:

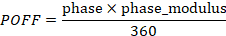

这段话的主要意思呢就是说:相位是以这个系数(modulus)为周期,即0~modulus-1表示0~360度。这个系数下面称为phase_modulus,则推算出相位控制字的公式为:

Phase:即为想要输出的相位,或者说与默认值得相位差,这里输入0-360即可;

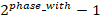

phase_modulus:相位系数为2phase_with-1 ;

;

phase_with:即相位位宽,在IP生成后的summary界面可以查到,第5章也会有标注。

5.IP核中的设置

6.相差180的实例截图